AMD は、AI および HPC において業界初のウルトラ イーサネット対応ネットワーク カードを発表しました。

Ultra Ethernet Consortium (UEC) は、仕様のバージョン 1.0 のリリースを 2024 年第 3 四半期から 2025 年第 1 四半期に延期しましたが、どうやら AMDは発表の準備ができている ウルトラ イーサネット データ センターにすぐに導入できる、AI データ センター用の真のネットワーク インターフェイス カードです。新しいユニットは AMD Pensando Pollara 400 で、AI ワークロードのパフォーマンスが最大 6 倍向上することが約束されています。

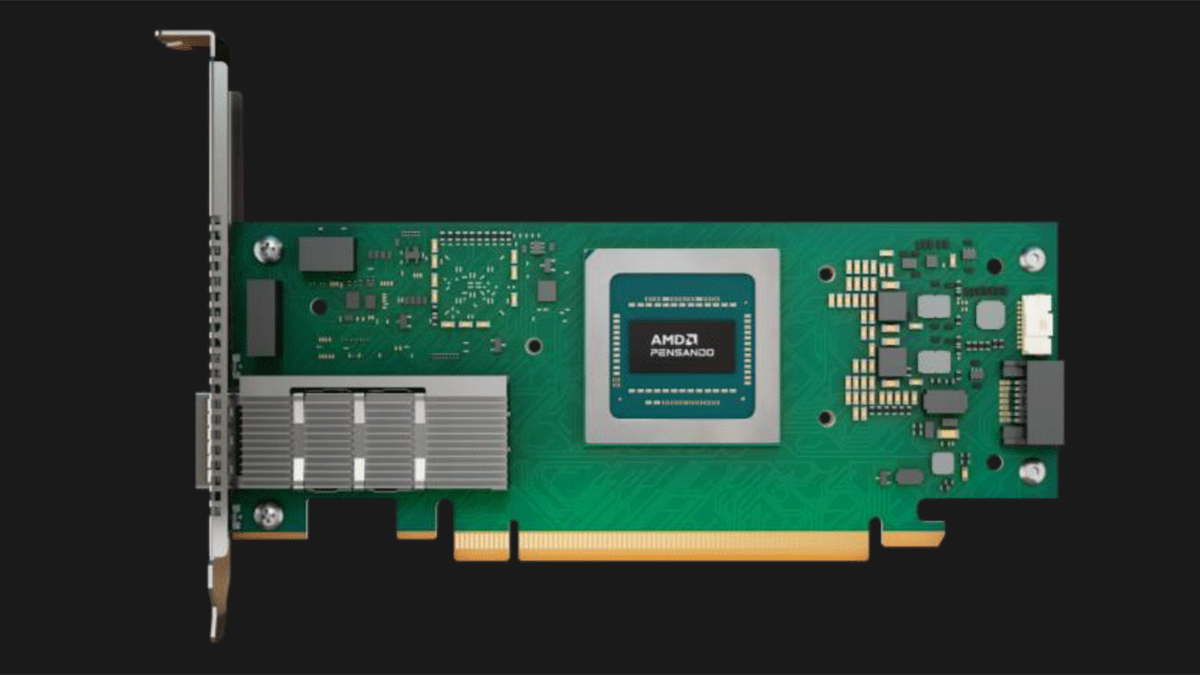

AMD Pensando Pollara 400 は、同社の Pensando 部門によって設計されたプロセッサをベースにした 400GbE ウルトラ イーサネット カードです。ネットワーク プロセッサは、プログラム可能なハードウェア パイプライン、プログラム可能な RDMA トランスポート、プログラム可能な輻輳制御、および通信ライブラリ アクセラレーションを備えています。 NIC は第 4 四半期にテストされ、ウルトラ イーサネット コンソーシアムが UEC 1.0 仕様を正式にリリースした直後の 2025 年前半に商用化される予定です。

AMD Pensando Pollara 400 AI NIC は、以下のために設計されています。 最適化する いくつかの高度な機能による AI および HPC ネットワーク。その主要な機能の 1 つはインテリジェント マルチパスであり、データ パケットを最適なパスに動的に分散してネットワークの輻輳を回避します。 グリッド 全体的な効率を向上させます。 NIC にはパスベースの輻輳制御も含まれており、一時的に輻輳したパスからデータをリダイレクトして、高速データの継続的なフローを確保します。

Pollara 400 は、高速フェイルオーバーを提供する革新的なソリューションです。つまり、ネットワーク障害を非常に迅速かつ効果的に検出して防止できます。これにより、グラフィックス プロセッシング ユニット (GPU) 間の通信が中断されなくなります。これは、高度な処理を必要とするアプリケーションにとって非常に重要です。 パフォーマンス そして継続的な可用性。 Pollara 400 は、シームレスな GPU 間通信を保証することで、堅牢なパフォーマンスを提供すると同時に、人工知能 (AI) クラスターの利用を最適化し、パフォーマンスに悪影響を与える可能性のある遅延を最小限に抑えます。 起訴 データの。

Pollara 400 のこれらの高度な機能は、AI インフラストラクチャの拡張性と信頼性を大幅に向上させる可能性があるため、特に有望です。これにより、このソリューションは、効率性と継続性が求められる大規模な導入に最適になります。 サービス それらは最も重要です。

並行して、ウルトラ イーサネット コンソーシアムの成長は、 テクノロジー 高度なネットワーキング。 2024 年 3 月の 55 名から大幅に増加した 97 名のメンバーを擁するこのコンソーシアムは、UEC 1.0 仕様の策定に取り組んでいます。この仕様は、 テクノロジー イーサネットは、パフォーマンスと機能の点でユビキタスであり、人工知能 (AI) およびハイ パフォーマンス コンピューティング (HPC) ワークロードの要求を満たします。

新しい UEC 1.0 仕様は、可能な限り再利用することで恩恵を受けます。 テクノロジー オリジナルのイーサネット。これにより、新しいテクノロジーのコスト効率の高い開発と展開が保証されるだけでなく、市場でのスムーズな導入に不可欠な既存のインフラストラクチャとの相互運用性も保証されます。

さらに、UEC 1.0 仕様には、AI と HPC 用の差別化されたプロファイルが含まれます。これらのタイプのワークロードにはいくつかの類似点がありますが、ニーズと特性には大きな違いもあります。したがって、それぞれの効率を最大化するために、AI と HPC の固有の要件に特に適合する個別のプロトコルが開発されます。これにより、組織はテクノロジー インフラストラクチャを最大限に活用し、パフォーマンスを最適化し、 ソリューションは幅広い用途に適しています そしてシナリオ。