AMD 在 AI 和 HPC 领域推出业界首款支持超以太网的网卡。

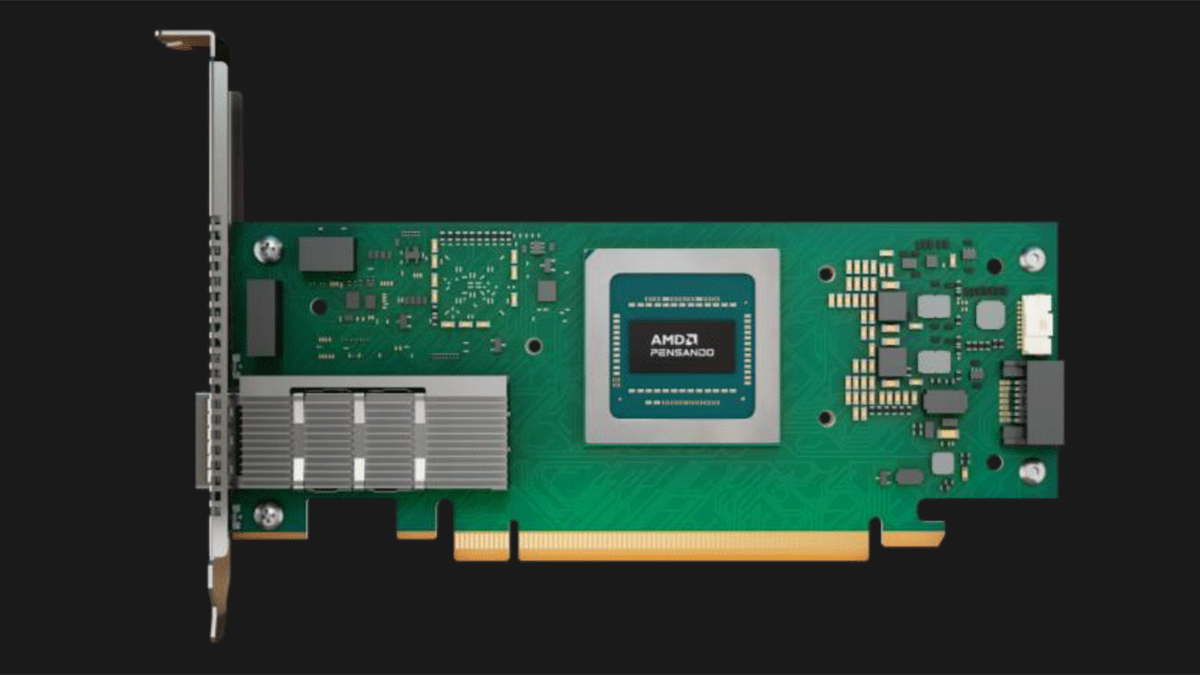

超以太网联盟 (UEC) 已将规范 1.0 版本的发布时间从 2024 年第三季度推迟到 2025 年第一季度,但看来 AMD 准备宣布 适用于人工智能数据中心的真正网络接口卡,可部署在超以太网数据中心中。新设备是 AMD Pensando Pollara 400,它有望将 AI 工作负载的性能提升六倍。

AMD Pensando Pollara 400 是一款 400GbE 超以太网卡,基于该公司 Pensando 部门设计的处理器。该网络处理器具有可编程硬件管道、可编程 RDMA 传输、可编程拥塞控制和通信库加速功能。该NIC将于第四季度进行测试,并于2025年上半年,即超以太网联盟正式发布UEC 1.0规范之后商用。

AMD Pensando Pollara 400 AI NIC 专为 优化 AI 和 HPC 网络通过多种先进功能实现。其主要功能之一是智能多路径,可在最佳路径上动态分配数据包,避免网络拥塞。 网格 并提高整体效率。 NIC 还包括基于路径的拥塞控制,可将数据从暂时拥塞的路径重定向,以确保高速数据的连续流动。

Pollara 400 是一种创新的解决方案,可提供快速故障转移,这意味着它可以非常快速有效地检测和预防网络故障。这可确保图形处理单元 (GPU) 之间的通信保持不间断,这对于需要高吞吐量的应用程序至关重要 表现 和持续可用性。通过确保 GPU 到 GPU 的无缝通信,Pollara 400 提供了强大的性能,同时优化了人工智能 (AI) 集群的利用率并最大限度地减少了可能对性能产生负面影响的延迟。 检控 的数据。

Pollara 400 的这些先进功能特别有前途,因为它们有可能显着提高人工智能基础设施的可扩展性和可靠性。这使得该解决方案非常适合大规模部署,其中的效率和连续性 服务 它们至关重要。

与此同时,超以太网联盟的发展反映了人们对以太网发展的兴趣和扩张。 技术 先进的网络。该联盟目前拥有 97 名成员,较 2024 年 3 月的 55 名成员大幅增加,目前正在制定 UEC 1.0 规范。该规范旨在扩展 技术 以太网在性能和功能方面无处不在,可以满足人工智能 (AI) 和高性能计算 (HPC) 工作负载的需求。

新的 UEC 1.0 规范将受益于尽可能多的重用 技术 原始以太网。这不仅确保了新技术的开发和部署具有成本效益,而且还确保了与现有基础设施的互操作性,这对于市场的顺利采用至关重要。

此外,UEC 1.0 规范将包括针对 AI 和 HPC 的差异化配置文件。尽管这些类型的工作负载有一些相似之处,但它们的需求和特征也存在显着差异。因此,为了最大限度地提高每个协议的效率,将开发专门满足人工智能和高性能计算独特要求的单独协议。这将使组织能够充分利用其技术基础设施,优化性能并确保 解决方案适用于广泛的应用 和场景。